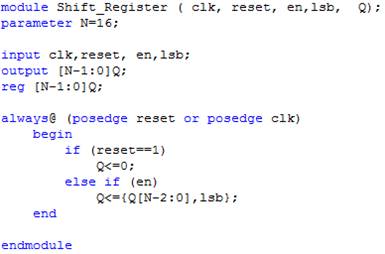

Incidentally, it's also why open source FPGA tools aren't really a thing. In more complex designs - especially those with multiple clocks - then you do need to very carefully consider how signals cross clock domains, and you must create a timing constraints file (.SDC) which describes the relationships between your clocks and other important signals. Provided the tool's timing analyser indicates positive setup & hold slack, you compile your code for the correct variant of the device, and you use that device within the manufacturer's recommended spec, then your design will meet timing. The synthesis tool contains a timing model of the FPGA, which the manufacturer guarantees across voltage, temperature and part-to-part variation. I speak VHDL, not Verilog, but the basic premise is the same - in synchronous logic, any reference to the state of a signal means the state of that signal at the instant just before the active clock edge. The following code simulates just fine in iverilog: /* lfsr.No, it's OK - this is why vendors' synthesis tools are used. I implemented it exactly how it was mentioned in Ciletti book: #100 $monitor("This is the cllk %b %b %b",tp_coeff,Y,clk) I tried implementing LFSR using Verilog, but I am unable to get the output properly, please check the verilog code for both module and test bench below:- //LFSR.v

0 kommentar(er)

0 kommentar(er)